# **DS1482** LLAS 1-Wire Level Shifter and Line Driver with Load Sensor

## www.maxim-ic.com

# FEATURES

- Works with All iButtons<sup>®</sup> and 1-Wire<sup>®</sup> Devices

- Communicates at Regular and Overdrive 1-Wire Speed (Host-Dependent)

- Separate Interface Power Supply to Level Shift to Non-5V Systems

- External Strong-Pullup Control Pin can be Used to Provide Low-On-Resistance-High **Current Power Source**

- Load Sensor to Detect when Strong-Pullup Power Delivery is no Longer Needed

- Power Delivery DONE Signal can be Connected to Host Interrupt

- Low-Cost 16-Pin SO Surface-Mount Package

- Operating Temperature Range: -40°C to +85°C

### PIN ASSIGNMENT Vccq 1 [ $\cap$ N.C. 2 SPU 31 START 4 TXD N.C. 61 GND 7 N.C. N.C. 8 9 **SO-16** DS14825 SO-16, Tape-and-Reel DS1482 bytact the factory for versions with different shal polarities.

# DESCRIPTION

The DS1482 is a simple 1-Wire line driver with load sensor and level shifter, designed to function as an interface between a 3V host system and a 1-Wire system that runs on 5V. Two supplies are provided, a 5V supply for the 1-Wire operations ( $V_{CC}$ ) and an interface supply ( $V_{CCO}$ ). The DS1482 can connect directly to a synchronous serial port if it supports the appropriate bit rates to generate 1-Wire timing.

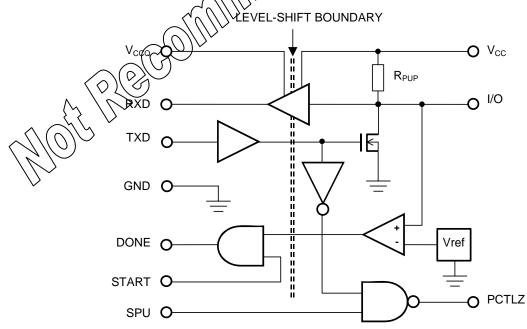

Figure 1 shows the DS1482 block diagram. TXD is buffered and controls an N-channel transistor, which drives the 1 Wire pin I/O low, e.g., to initiate a time slot. The logic level of the I/O pin is returned through a figure 3 shows the RXD pin for the host processor to read. Figure 3 shows the relationship of these signals in case of a 1-Wire read time slot.

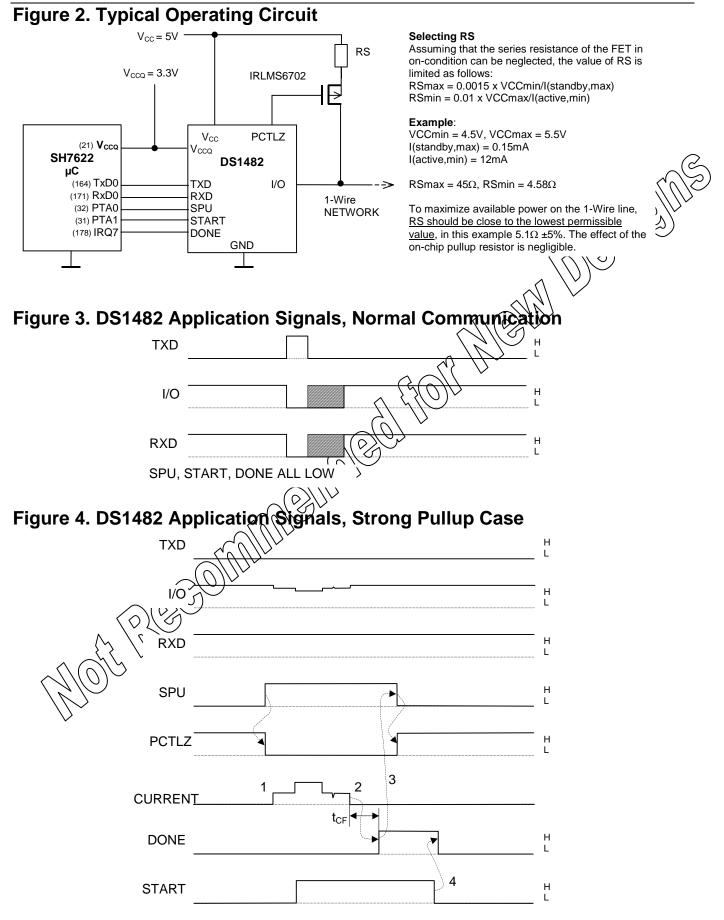

The SPU input generates a control signal (PCTLZ) for an external low-impedance PMOS transistor (Figure 2) that bypasses the 1-Wire pullup resistor ( $R_{PUP}$ ) to provide power for 1-Wire devices with a high-load current. PCTLZ is gated by the inverted TXD signal. This prevents a high through-current in case TXD and SPU are high at the same time.

The DS1482 contains a high-precision comparator because it is important for the host micro to know when the high load on the 1-Wire side is no longer active. As shown in Figure 4, the high current load causes a small drop of the voltage on the I/O pin. The comparator detects when the high current phase ends, and enables DONE after the deglitching time t<sub>CF</sub> is over. The START signal allows the host micro to selectively enable DONE.

| PIN         | NAME             | FUNCTION                                                                                |

|-------------|------------------|-----------------------------------------------------------------------------------------|

| 1           | V <sub>CCQ</sub> | Operating voltage for all circuitry that connects to the controlling                    |

|             |                  | microprocessor (TXD, RXD, START, SPU, DONE pins).                                       |

| 3           | SPU              | This line is used to control the external strong pullup function. When SPU is           |

|             |                  | low, the strong pullup (PCTLZ) is high. When SPU is high and TXD is low,                |

|             |                  | PCTLZ is low.                                                                           |

| 4           | START            | This line acts as an enable control for the DONE pin. If START is high, then            |

|             |                  | DONE reflects the filtered digital output of the current-sense comparator. If           |

|             |                  | START is low, then DONE is low.                                                         |

| 5           | TXD              | When TXD is low, the I/O pin is pulled resistively to $V_{CC}$ . When TXD is $\sqrt{2}$ |

|             |                  | high, the 1-Wire bus is pulled to GND (for write-0, write-1, read, and reset            |

|             |                  | low times).                                                                             |

| 7           | GND              | Ground Reference for $V_{CCQ}$ , $V_{CC}$ , 1-Wire                                      |

| 10          | I/O              | 1-Wire Data                                                                             |

| 12          | RXD              | This line returns the digital state of the 1-Wire bus, level-shifted to swing           |

|             |                  | between $V_{CCQ}$ and GND.                                                              |

| 13          | DONE             | This line is high only when the buffered, filtered digital output from the              |

|             |                  | current-sense comparator indicates that the downstream 1-Wire slave device              |

|             |                  | is no longer sinking high current. This signal is enabled if START is high.             |

| 14          | PCTLZ            | Active-low control pin for an external low-on-resistance, high-current                  |

|             |                  | supply. This signal typically controls the sate of a P-channel MOSFET. This             |

|             |                  | signal is low when SPU is high and TXD is low.                                          |

| 16          | V <sub>CC</sub>  | Operating voltage for all circuity that connects to the 1-Wire environment              |

|             |                  | (I/O and PCTLZ pins).                                                                   |

| 2, 6, 8, 9, | N.C.             | Not Connected                                                                           |

| 11, 15      | IN.C.            | Not Connected                                                                           |

# Figure 1. Block Diagram

\_\_\_\_

- **Point 1:** The 1-Wire slave device starts drawing current (internal micro or numeric processor is running). The strong pullup (SPU) must be activated before the high current phase begins.

- **Point 2:** The 1-Wire slave device no longer draws current. After the deglitching time  $(t_{CF})$  is over, the DONE signal turns high. The START signal must be activated no later than  $t_{SD}$  before  $t_{CF}$  is over. Typically START is activated shortly after SPU, but not before the 1-Wire slave device has started drawing high current.

- **Point 3:** As soon as the DONE signal is high, the host micro ends the strong pullup by changing SPU to low.

- **Point 4:** While the DONE signal is high, the host micro changes START to low; this may occur simultaneously with the state change of SPU or later. When START changes to low, DONE becomes low.

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage to GND (All Pins) Combined Source/Sink Current (All Pins) Operating Temperature Range Junction Temperature Storage Temperature Range Lead Temperature (Soldering) -0.5V, +6.0V 20mA -40°C to +85°C +150°C -55°C to +125°C See IPC/JEDEC 020A

\* This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

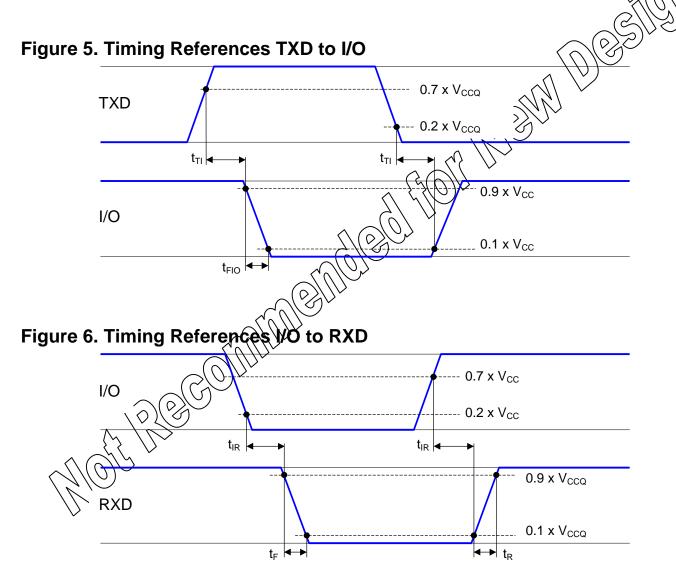

### ELECTRICAL CHARACTERISTICS $(V_{CC} = 4.5V \text{ to } 5.5V, V_{CCQ} = 3.0V \text{ to } 3.6V; T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ MIN **CONDITIONS** PARAMETER SYMBOL MAX UNITS Supply Current 150 ICC μA Supply Current 100 Icco μA $V_{CC}$ , $V_{CCQ}$ rising from 0 Supply Ramp-up Time (System to V<sub>CCMIN</sub> and V<sub>CCOMIN</sub> t<sub>RCC</sub> μs Requirement) respectively 1-Wire Pullup 850 1650 R<sub>PUP</sub> Ω Resistor **INPUT PINS SPU, START, TXD** $0.7 \text{ x } V_{CCO}$ V Input High Voltage $V_{IH}$ V Input Low Voltage VIL $0.2 \times V_{CCO}$ Measured with either 0V $\nabla \mathbf{r} \mathbf{W}_{CCO}$ on the pin Input Leakage 3 μA $I_{LP}$ (Note 1) No DC load on I/O; see Delay TXD to I/O 100 ns Figure 5 (Note 2) I/O PIN (1-WKRE) Output Low/Voltage 0.4 Vor 100µA load V Output High Woltage No DC load V VOH V<sub>CC</sub> Pin Leakage Current (Note 3) +1 $I_{LP}$ -1 μA Input High Voltage $0.7 \times V_{CC}$ V<sub>IH</sub> V Input Low Voltage $0.2 \ x \ V_{CC}$ $V_{IL}$ V 0.995 x 0.998 x Comparator V V<sub>REF</sub> 0.99 x V<sub>CC</sub> $V_{CC}$ V<sub>CC</sub> **Reference Voltage Output Fall Time** $0.9 \ge V_{CC}$ to $0.1 \ge V_{CC}$ 45 150 t<sub>FIO</sub> ns (50pF Load)

|                                    |                 |                                                |                                           |           |     | DS1482        |

|------------------------------------|-----------------|------------------------------------------------|-------------------------------------------|-----------|-----|---------------|

| PARAMETER                          | SYMBOL          | CONDITIONS                                     | MIN                                       | TYP       | MAX | UNITS         |

| OUTPUT PIN RXD                     |                 |                                                |                                           |           |     |               |

| Output-Low Voltage                 | V <sub>OL</sub> | 100µA load                                     |                                           |           | 0.4 | V             |

| Output-High Voltage                | V <sub>OH</sub> | -100µA load                                    | V <sub>CCQ</sub> - 0.5V                   |           |     | V             |

| Output Rise Time<br>(50pF Load)    | t <sub>R</sub>  | 0.1 x $V_{CCQ}$ to 0.9 x $V_{CCQ}$             |                                           |           | 50  | ns            |

| Output Fall Time<br>(50pF Load)    | t <sub>F</sub>  | 0.9 x V_{CCQ} to 0.1 x V_{CCQ}                 |                                           |           | 50  | ns            |

| Delay I/O to RXD<br>(50pF Load)    | t <sub>IR</sub> | See Figure 6 (Note 2)                          |                                           |           | 100 | ns            |

| <b>OUTPUT PIN PCTL</b>             | Z               |                                                |                                           |           | <   | $\frac{1}{2}$ |

| Output-Low Voltage                 | V <sub>OL</sub> | 100µA load                                     |                                           |           | 0.4 |               |

| Output-High Voltage                | V <sub>OH</sub> | -100µA load                                    | V <sub>CC</sub> - 0.5V                    |           |     |               |

| Output Rise Time<br>(50pF Load)    | t <sub>R</sub>  | 0.1 x V <sub>CC</sub> to 0.9 x V <sub>CC</sub> |                                           | $\langle$ | 060 | ns            |

| Output Fall Time<br>(50pF Load)    | t <sub>F</sub>  | 0.9 x V <sub>CC</sub> to 0.1 x V <sub>CC</sub> |                                           | M         | 50  | ns            |

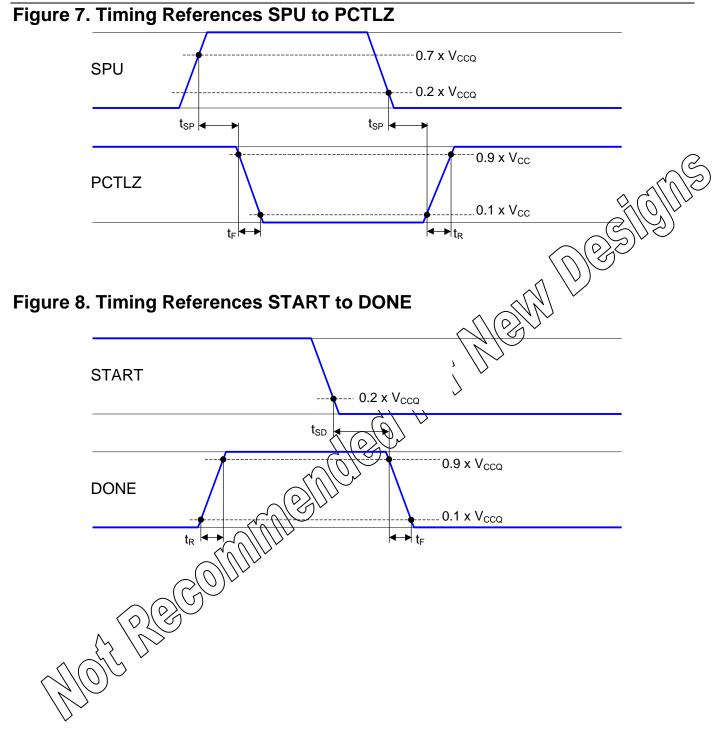

| Delay SPU to PCTLZ<br>(50pF Load)  | t <sub>SP</sub> | See Figure 7 (Note 4)                          |                                           | <u>y</u>  | 100 | ns            |

| <b>OUTPUT PIN DONE</b>             | C               |                                                | $\langle \langle \langle \rangle \rangle$ | •         |     | 1             |

| Output-Low Voltage                 | V <sub>OL</sub> | 100µA load                                     | $\langle 0 \rangle \rangle$               |           | 0.4 | V             |

| Output-High Voltage                | V <sub>OH</sub> | $-100\mu A$ load                               | V <sub>CCQ</sub> - 0.5V                   |           |     | V             |

| Output Rise Time<br>(50pF Load)    | t <sub>R</sub>  | 0.1 x V <sub>CCQ</sub> to 0 Driver             | V                                         |           | 50  | ns            |

| Output Fall Time<br>(50pF Load)    | t <sub>F</sub>  | 0.9 x Vacan Q. X VCCQ                          |                                           |           | 50  | ns            |

| Delay I/O to DONE<br>(50pF Load)   | t <sub>CF</sub> | SFART at V <sub>CCQ</sub> (Note 5)             | 128                                       |           | 500 | μs            |

| Delay START to<br>DONE (50pF Load) | t <sub>SD</sub> | See Figure 8                                   |                                           |           | 100 | ns            |

Note 1: The input pins have a weak pulldown.

- Note 2: For OD read of write-1 time slots, TXD should be pulsed high for 1.28µs. The window for sampling RXD begins 1.8µs after TXD has turned high and ends 2.05µs after TXD has turned high RXD must be sampled inside this window. Correct sampling can be achieved with the particular recommended microcontroller Hitachi SH7622 if the peripheral module operating trequency PΦ is higher or equal to 22MHz.

- Note 3. Measured either with  $V_{CC}$  on the pin and TXD low or with 0V on the pin and TXD high. This parameter is guaranteed by design, and is not production tested.

- **Note 4:** The PCTLZ signal is gated by TXD. The PCTLZ output is only low if TXD is low.

- **Note 5:** Characteristic of the glitch-eating filter on the output of the load-sensing comparator, i.e., an event where the downstream 1-Wire slave device is sinking high current, ceases sinking the current for less than this amount of time, and resumes sinking the current does not generate high level on DONE; DONE goes high this amount of time after the downstream 1-Wire slave device has ceased sinking high current.